250x250

반응형

Notice

Recent Posts

Recent Comments

Link

| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | |||

| 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 26 | 27 | 28 | 29 | 30 | 31 |

Tags

- 자동차sw

- 퀀트

- 확률

- 파이썬

- 비트코인

- Cloud

- GeorgiaTech

- AWS

- 암호화폐

- 자동매매

- it

- 토플

- toefl writing

- 클라우드

- 개발자

- 토플 라이팅

- 백트레이더

- can

- Bitcoin

- 백테스트

- TOEFL

- backtest

- python

- 프로그래밍

- AUTOSAR

- 블록체인

- backtrader

- 오토사

- probability

- 아마존 웹 서비스

Archives

- Today

- Total

Leo's Garage

AURIX™ MCU: Determining the clock tree path from source to derive SPI bus baud rate - KBA237424 본문

Embedded/AURIX

AURIX™ MCU: Determining the clock tree path from source to derive SPI bus baud rate - KBA237424

LeoBehindK 2023. 6. 27. 21:59728x90

반응형

* 아래 글은 제가 Infineon Developer Community에 작성한 내용입니다.

외부 오실레이터 또는 백업 오실레이터에서 시작하여 QSPI 주변장치에 도달하는 지점까지 QSPI에 대한 전체 클럭 트리가 그림 1에 나와 있습니다.

QSPI 개요 다이어그램(그림 2)에서 fPER은 그림 1에서 도출한 fQSPI이며, 이는 QSPI 모듈 시프트 엔진의 주파수입니다. 따라서 시프트 엔진은 fSPB와 독립적인 별도의 주파수 영역(즉, fPER)에 배치됩니다.

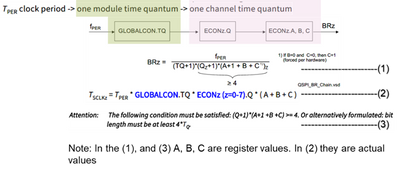

SPI bus baud 속도는 GLOBALCON 및 ECON 레지스터를 구성하여 그림 3과 같이 fPER에 의해 결정됩니다. fPER는 먼저 글로벌 디바이더를 통과한 다음 채널별 디바이더를 통과하여 SPI 채널에 원하는 baud 속도에 도달합니다.

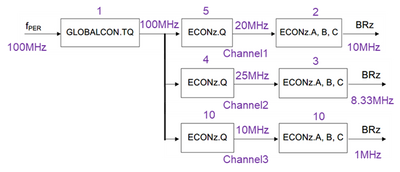

그림4는 어떻게 SPI bus baud rate가 결정되는지에 대한 예제를 보여준다.

이 방법을 사용하면 Clock 트리를 모든 주변 장치에 대해 따라갈 수 있습니다.

이 KBA는 AURIX™ TC3xx 사용 설명서의 기술 개념과 스냅샷을 사용합니다. 그러나 이는 다음 시리즈의 AURIX™ MCU에만 적용됩니다:

AURIX™ TC2xx series

AURIX™ TC3xx series

728x90

반응형

'Embedded > AURIX' 카테고리의 다른 글

| [AURIX] SCR(Standby Controller) 개요 (0) | 2023.11.27 |

|---|---|

| AURIX TC3xx EVADC Self Diagnostic - Converter Diagnostics (0) | 2023.07.20 |

| MCAL IRQ과 AUTOSAR OS ISR 연결 (0) | 2023.07.18 |

| AURIX™ MCU: PWM signal generation using CCU6 – KBA236919 (0) | 2023.06.27 |

| TC387 PMS(Power Management System) - PBIST와 internal Monitor (0) | 2023.02.08 |

Comments